文章编号:1674-2974(2020)02-0110-06

DOI: 10.16339/j.cnki.hdxbzkb.2020.02.015

# 一种低功耗高精度电流比较器的设计

余飞1,高雷1,王春华2

(1.长沙理工大学 计算机与通信工程学院,湖南 长沙 410114; 2.湖南大学 信息科学与工程学院,湖南 长沙 410082)

摘 要: 针对传统电流比较器功耗高、精度低等问题,提出了一种基于 Wilson 电流源的 CMOS 电流比较器电路. 它由 Wilson 电流源、差分放大器和输出增益级 3 部分组成. 由于 Wilson 电流源具有较好的恒流特性以及较高的输出阻抗,所以该电流比较器具有较高的比较精度和低延迟的传播特性. 采用 TSMC  $0.18\,$  CMOS 工艺 HSPICE 模型参数对该电流比较器的性能进行了模拟,该电路具有较高的比较精度,当参考输入电流为  $5\,$  nA 时,电路正常工作. 当输入差分电流为  $1\,$   $\mu$ A 时延迟为  $2.2\,$  ns,电路的功耗在 TT(typical)工艺角下为  $95\,$   $\mu$ W. 结果表明,该 CMOS 电流比较器具有较大的速度/功耗比,性能受工艺偏差影响较小,适用于高速、低功耗电流模集成电路.

关键词:Wilson 电流源;低功耗;高精度;电流比较器;比较器电路

中图分类号:TN433

文献标志码: A

# Design of a Low Power Consumption and High Precision Current Comparator

#### YU Fei<sup>1†</sup>, GAO Lei<sup>1</sup>, WANG Chunhua<sup>2</sup>

School of Computer and Communication Engineering, Changsha University of Science and Technology, Changsha 410114, China;

College of Computer Science and Electronic Engineering, Hunan University, Changsha 410082, China)

**Abstract:**A CMOS current comparator circuit based on Wilson current source is proposed to solve the problems of high–power consumption and low precision of traditional current comparator. It consists of Wilson current source, differential amplifier and output gain stage. Because Wilson current source has better constant current characteristics and higher output impedance, the current comparator has higher comparative accuracy and low delay propagation characteristics. The HSPICE model parameters of TSMC 0.18 CMOS process are used to simulate the performance of the current comparator. The circuit has a high precision of 5 nA. When the input differential current is 1  $\mu$ A, the delay is 2.2 ns, and the power consumption of the circuit is 95  $\mu$ W at TT (typical) process angle. The results show that the CMOS current comparator has a high speed/power ratio, and its performance is less affected by the process deviation which is suitable for high–speed and low–power current–mode integrated circuits.

Key words: Wilson current source; low power; high precision; current comparator; comparator circuits

<sup>\*</sup> 收稿日期:2019-03-15

**基金项目:**国家自然科学基金资助项目(61504013,61571185),National Natural Science Foundation of China(61504013,61571185);湖南省自然科学基金资助项目(2019JJ50648),Natural Science Foundation of Hunan Province(2019JJ50648)

作者简介:余飞(1984一),男,安徽安庆人,长沙理工大学讲师,博士

<sup>†</sup>通讯联系人,E-mail:yufeiyfyf@csust.edu.cn

随着集成电路技术的发展,高性能的电路设计成为设计难题 [1-2]. 电流模电路相比于电压模电路具有更好的传输特性,在高频工作时不需要考虑杂散电容和寄生电容的影响[3-5],并且能够在低电源电压下工作,在静态工作点固定的情况比电压模电路具有更好的输入特性.

电流比较器作为 ADC(Analog -to -Digital Converter)的接口,负责将模拟信号转化成数字信号,所以电流比较器的性能好坏对 ADC 的性能有很大影响. 通常电流比较器在 ADC 中不是单独存在,当其功耗过高时会严重影响到整个ADC 的性能. 对于电流比较器我们通常关心的是它的功耗和传播延迟,因此,设计低功耗低延迟的电流比较器是非常重要的.

电流比较器通常分为两类<sup>[6]</sup>:第1类是将输入电流与电路的静态工作电流进行比较,电路的输入级负责将电流转换为可供增益级处理的电压,作为反馈控制电路的阻抗特性和幅频特性,并且能够改善电路的传输特性,增益级使得电路能够产生轨对轨输出电压.该类型电路可以用于简单的电流修正,如共模反馈电路.第2类是比较双端输入电流,该结构通常是由差分结构组成,常用到差分放大器,差分放大器可以抑制共模噪声并且提高电路的处理精度,但该类型电路的缺点是提高了电路的复杂性和流片的面积与成本,通常该结构适用于并行的 ADC.

电流比较器的输入级通常可以通过简单的电流镜来实现,但由于电流镜有限的输出阻抗和电流传递误差,使得电路的优化通常需要改善电路的恒流特性[<sup>7-8]</sup>. 最早的电流比较器是由 Traff<sup>90</sup>提出的基于源随级(共漏放大器)的电流比较器,它具有较小的输入阻抗,所以电路处理速度较快,由于支路使用的MOS 管的数量较少,能够工作在低电源电压(不需要额外的电压偏置电路)下. 但是该结构有个明显的缺点,当动态范围内小部分信号输入时可能存在死区,同时,该电路具有较为明显的背栅效应(阈值电压的变化).

为了改善电路的传输特性,Sridhar等人<sup>110</sup>使用cascade结构作为输入级,该结构具有较高的输出阻抗,由于 MOS 管的屏蔽效应,使得恒流特性得到了较为可观的改善,但该电路无法抑制沟道调制效应,并且在低电源电压(通常为 1 V 或更低)且不使用额外的电压偏置的前提下难以使 MOS 管全部工作于饱和区域.

为了进一步解决由于沟道调制效应带来的电流 传输问题,Badal等人III提出使用 Wilson 电流源作为 输入,并使用推挽放大器和反相器获得轨对轨输出电压.由于 Wilson 电流源良好的恒流特性,并且能够工作在亚阈值区 (栅源电压略微低于阈值电压),该结构被广泛用作输入级.但该结构也存在两点不足,第一,当输入小信号时(比如输入电流差为 100 nA),单级放大不足以输出轨对轨电压;第二,该结构不能比较双支路差分电流.针对该结构出现的问题,本文提出了一种改进型的基于 Wilson 电流源的电流比较器.

### 1 电路原理

### 1.1 Wilson 电流源

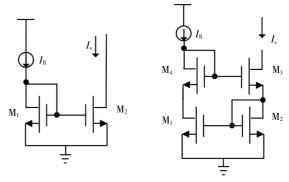

Wilson 电流源如图 1(a)所示,该结构具有较大的输出阻抗,M<sub>1</sub>和 M<sub>2</sub>组成了简单的电流镜,M<sub>3</sub>作为 Wilson 电流源的反馈提高了该结构的输出阻抗.输出阻抗由公式(1)给出:

$$r_{\text{out}} = \frac{1}{g_{\text{M2}}} + r_{\text{d3}} \left[ 1 + \frac{g_{\text{M3}}}{g_{\text{M2}}} \left( 1 + g_{\text{M1}} r_{\text{ds1}} \right) \right]$$

(1)

式中: $g_{Mx}$ , $x = \{1,2,3\}$ 为 MOS 管的跨导; $r_{dst}$  为 MOS 管的导通电阻. 假定  $g_{M1} = g_{M2} = g_{M3}$ ,且  $g_{M1}r_{ds1} \ge 1$ ,该式可以表达为  $r_{out} = r_{ds3}g_{M1}r_{ds1}$ ,该输出阻抗远大于简单电流镜的输出阻抗( $r_{out} = r_{ds2}$ ),由于该结构不能实现真正的恒流特性( $M_1$  与  $M_2$  的漏源电压不同),故有关文献提出了另一种改进型结构如图 1(b)所示,当  $M_3$  和  $M_4$  的栅源电压相等时,即  $V_{gs3} = V_{gs4}$ ,该结构的传输特性由公式(2)给出:

$$\frac{(W/L)_3}{(W/L)_4} = \frac{(W/L)_2}{(W/L)_1} \tag{2}$$

式中:W 和 L 分别为 MOS 管沟道的宽度和长度.

不难看出,改进型的 Wilson 电流源消除了沟道调制效应,是一种高精度的电流源.

(a) Wilson 电流源

(b) 改进型 Wilson 电流源

图1 电流源电路

Fig.1 Current source circuit

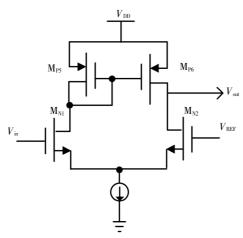

#### 1.2 差分放大器

为了比较双端输入电流,将差分放大器作为中

间级,原理如图 2 所示. 最简单的差分级包含两个输入 MOS 管,一个尾电流源和电流镜负载,该结构的增益由公式(3)表述:

$$A = g_{\text{N1,N2}}(r_{\text{dsN1,2}} \parallel r_{\text{dsP5,6}})$$

(3)

式中: $r_{dsN1,2}$ 、 $r_{dsP5,6}$ 分别为  $M_{N1,2}$  和  $M_{P5,6}$  的导通电阻.

图 2 一种结构简单的差分放大器 Fig.2 A simple differential amplifier

为了得到轨对轨输出电压,通常希望差分级的增益足够大,但通过增加增益发现只能增大  $g_{MNI,N2}$  或是增大输出电阻. 忽略电流源电阻,  $V_{out}$  端的时间常数由公式(4)给出:

$au \approx (C_{\rm gdN2} + C_{\rm gdP6} + C_{\rm dbP6} + C_{\rm dbN2})(r_{\rm dsN2} \parallel r_{\rm dsP6})$  (4) 式中:  $C_{\rm gdN2}$ 、 $C_{\rm gdP6}$  分别为  $M_{\rm N2}$  和  $M_{\rm P6}$  的栅漏电容;  $C_{\rm dbN2}$ 、 $C_{\rm dbP6}$  分别为  $M_{\rm N2}$  和  $M_{\rm P6}$  的漏极到衬底电容; $r_{\rm dsN2}$ 、 $r_{\rm dsP6}$  分别为  $M_{\rm N2}$  和  $M_{\rm P6}$  的导通电阻.

增加增益后,不难发现该点的时间常数会同时增加,时间常数的增加意味着电路传播延迟的增加,这与设计的初衷是相违的,所以输出需要经过输出增益级来改善输出特性.

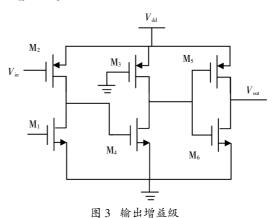

#### 1.3 输出增益级

对于输出小信号而言,输出增益级显得尤为重

要,输出增益级如图 3 所示,输出增益级由 2 个共源放大器 M<sub>1</sub>、M<sub>4</sub> 和一个 CMOS 反相器组成,输出信号经过共源放大器放大,最终通过 CMOS 反相器对信号进行处理.对于单级的共源放大器而言,每一级的增益可以由公式(5)表示:

$$A_1 = g_{M1,4} r_{out} \tag{5}$$

式中: $r_{out}$  对应于每个单级放大器的输出阻抗( $r_{ds1} \parallel r_{ds2}$  和  $r_{ds3} \parallel r_{ds4}$ , $r_{ds1-4}$  分别为  $M_{1-4}$  的导通电阻); $g_{M1,4}$  为输入管  $M_1$  和  $M_4$  的跨导. 不难看出,只需要增加输出阻抗便可以得到较高的开环增益.

对于 CMOS 反相器而言,当  $M_4$  的漏极电压为高电压时,输出为  $V_{ss}$  (在本设计中  $V_{ss}$  接地),相应地,当  $M_4$  的漏极电压为低电压时( $V_{d4} - V_{thN} < 0$ ),输出为  $V_{DD}$ ,当  $V_{d4}$  接近  $V_{thN}$  (NMOS 的阈值电压)时, $M_6$  进入亚阈值状态,其导通电阻远远大于  $M_5$  的导通电阻,其最终的输出电压由公式(6)给出:

$$V'_{\text{out}} = \frac{r_{\text{s6}}}{r_{\text{ds6}} + r_{\text{ds5}}} V_{\text{DD}} \tag{6}$$

式中:rs6 为 M6 的内阻.

Fig.3 Gain stage of output stage

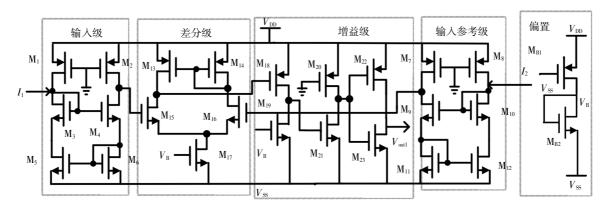

#### 1.4 基于 Wilson 电流源的电流比较器

本文提出的基于 Wilson 电流源的电流比较器电路原理图如图 4 所示.

图 4 提出的基于 Wilson 电流源的电流比较器电路图

Fig.4 Circuit diagram of current comparator based on Wilson current source

该电路采用差分结构进行比较,由于 Wilson 电流镜作为输入级,该结构的输入阻抗为:

$$r_{\text{in,close}} \approx \frac{1/r_{\text{ds1}} + 1/(r_{\text{ds1}} + r_{\text{ds2}})}{g_{\text{M5}}g_{\text{M4}}}$$

(7)

式中: $g_{Mx}$ 和  $r_{dsx}$ 分别为 MOS 管的跨导与内阻,该结构的输入阻抗是较低的. 不难看出,该结构的输入阻抗能够通过增加  $M_5$  和  $M_4$  跨导减小.  $M_{22} \sim M_{23}$  作为电路的输出级,其输出阻抗为:

$$r_{\text{out}} \approx r_{\text{ds}22,23}$$

(8)

$$r_{\text{ds22,23}} = \frac{V_{\text{ds}}}{I_{\text{d}}} = \frac{1}{2K_{\text{N}}(V_{\text{gs}} - V_{\text{thN}})}$$

(9)

式中: $K_N$ 为 MOS 的导电因子.

从式(8)和式(9)可以看出,该电路的输出阻抗 主要由 M<sub>22</sub>~M<sub>23</sub> 的宽长比决定,晶体管尺寸能够有效 地增加电路的负载能力.

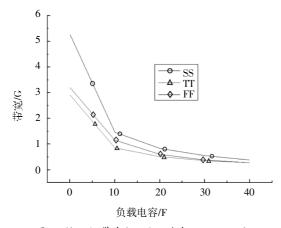

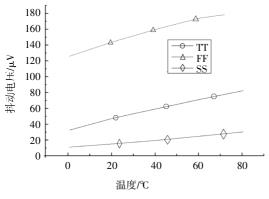

## 2 仿真结果

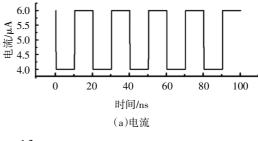

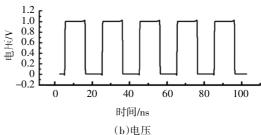

本文提出的电路主要结构为: $M_1 \sim M_6$ 和  $M_7 \sim M_{12}$ 组成的两个输入端, $I_1$ 为信号电流输入端, $I_2$ 为电流参考端, $M_{1-2}$ 和  $M_{7-8}$ 为输入端电路提供电流偏置, $M_{13} \sim M_{17}$ 组成了简单差分级, $M_{17}$ 为差放的尾电流源,通过改变其两条支路上电流变化以改变输出电压,该结构用于比较双端电流. $M_{18} \sim M_{23}$ 组成了输出增益级, $M_{18} \sim M_{21}$ 组成了两个共源放大器,而  $M_{22} \sim M_{23}$ 为反相器.最后简单的偏置电路由  $M_{B1}$ 和  $M_{B2}$ 组成.该电流比较器的瞬态仿真如图 5 所示. 当温度为  $40 \sim 100$ 、工艺为 100 TT,输入差分电流为 100 100 和 的时候,电路功耗在 100 TT 工艺角下的变化曲线如图 6 所示.

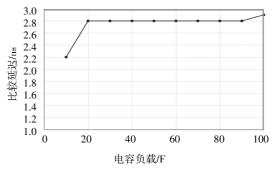

电路使用 Spectre 和 Hspice 进行仿真,并使用 TSMC 0.18 CMOS 工艺和 IC5141 进行布线,电源电压  $V_{DD}$  为 1 V,  $I_1$  端输入方波电流,其上升沿和下降 沿设置为 0.2 ns;  $I_2$  输入参考电流,输入参考电流通常为直流电流,在输入差分电流为 1  $\mu$ A 的情况下,该电路取得了 2.2 ns 的传播延迟,低于大多数已提出的电流比较器结构的传播延迟。该电路精度较高,当输入参考端电流为 5 nA 时能正常工作。表 1 给出了图 4 所示电路的 MOS 管参考尺寸比例,对于放大器负载而言,为了得到更高的输出摆幅,负载管的阻抗通常不能过大,所以在本设计中使用较大比例的 PMOS 负载,同时为了减小电路的传播延迟,放大器的输入管尺寸通常不会太大(考虑开环增益与传播延迟之间的折衷)。如图 7 所示,对于不同的负载大

小,输入级的带宽会有较大的不同,因此减小负载电容的大小是十分必要的.

图 5 电流比较器的瞬态仿真

Fig.5 Transient wave of current comparator

图 6 电路功耗(温度为 40 ℃, 工艺为 TT, 输入差分电流为 1 μA)

Fig.6 Circuit power consumption (temperature is 40  $^{\circ}$ C, process is TT and input differential current is 1  $\mu$ A)

表 1 图 4 所示电路中 MOS 管的参考宽长比

Tab.1 Width-to-length ratio of MOS transistors in the circuit shown in Fig.4

|                                                           | 0    |

|-----------------------------------------------------------|------|

| MOS 管                                                     | W/L  |

| $M_{3-6}, M_{9-12}, M_{22}, M_{23}$                       | 1:1  |

| $\mathbf{M}_{12}$ , $\mathbf{M}_{78}$ , $\mathbf{M}_{21}$ | 2:1  |

| $\mathbf{M}_{17}$ , $\mathbf{M}_{20}$                     | 3:1  |

| $\mathbf{M}_{13\sim14}$                                   | 10:1 |

| $ m M_{15-16}$                                            | 3:5  |

| $\mathbf{M}_{19}$                                         | 1:2  |

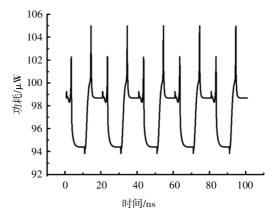

图 7 输入级带宽(不同工艺角 TT,FF,SS)

Fig.7 Bandwidth with input stage (different corner TT,FF and SS)

图 8 给出了因为电路不完全对称和电流源的有限阻抗所导致的尾电流源处抖动电压的大小. 表 2给出了近年来已提出的电流比较器的性能参数,包括功耗、延迟、电源电压、工艺类型;通过比较不难发现,本设计取得了较低的延迟,功耗也低于大多数结构(95 μW,TT 工艺角下,温度为 40 ℃). 对于文献[8]中提出的电路结构(采用 DCC II 作为输入级),尽管延迟很低,但电路结构过于复杂,其结构随着温度的变化,静态工作点漂移严重,对电路的实用性产生了较大的影响. 综合比较已提出的结构,本文中的基于Wilson 电流镜的电流比较器具有较小的功耗和延迟.

图 8 抖动电压(差分级尾电流源)

Fig.8 Offset voltage (different stage)

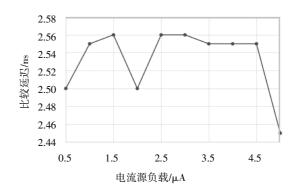

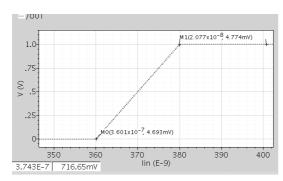

由于比较器负载通常为容性负载和有源负载, 图 9 和图 10 分别给出了比较延迟随着容性负载大小和电流源负载大小的变化曲线. 在不同负载情况 下,电路的比较延迟变化不大. 图 11 给出了当电流  $I_2$  为 5 nA 时,随着  $I_1$  变化, $V_{\text{out}}$  变化的 DC 曲线,该电路能够正常工作.

表 2 本文与已发表的电流比较器性能参数比较

Tab.2 Comparison of performance parameters

with published current comparators

| 参考文献 | 电源电压<br>V <sub>DD</sub> /V | 工艺尺寸<br>/μm | 功耗<br>/μW | 延迟( $I_{\rm in}/t_{ m delay}$ ) /( $\mu { m A \cdot ns^{-1}}$ ) |

|------|----------------------------|-------------|-----------|-----------------------------------------------------------------|

| [9]  | 1.8                        | 0.13        | 314       | 1/0.34                                                          |

| [7]  | 5                          | 2           | 930       | 1/4                                                             |

| [1]  | 3.3                        | 0.35        | 0.01      | 1/4                                                             |

| [5]  | 3                          | 1.2         | 300       | 1/7                                                             |

| [6]  | 1.8                        | 0.18        | 158       | 1/0.4                                                           |

| [8]  | 1                          | 0.35        | 30        | 1/15                                                            |

| 本文   | 1                          | 0.18        | 95        | 1/2.27                                                          |

图 9 比较延迟(随容性负载大小变化)

Fig.9 Compares delays (varying with value of capacitive loading)

图 10 比较延迟(随电流源负载大小变化)

Fig.10 Compares delays (varying with value of current source loads)

图 11 当电流  $I_2$  为 5 nA 时,随着  $I_1$  变化,  $V_{out}$  变化的 DC 曲线

Fig.11 The DC curve of  $I_1$  varies with  $V_{\text{out}}$  when the current  $I_2$  is 5 nA

## 3 结 论

本文提出了一种基于 Wilson 电流源的低功耗低延迟电流比较器. 首先介绍了几种典型的电流比较器,特别是基于改进电流源结构的电流比较器,并分析了 Wilson 电流源的特性. 所提出的电流比较器的传播延迟为 2.2 ns,功耗为 95 μW,其传播延迟低于大多数已提出的比较器,并且操作速度和功耗与先前的高速设计相当.

## 参考文献

- [1] 李远,周卫华,单旭.一种电路域加密通信方案[J]. 信息网络安全,2015,15(6):26—32.

- LI Y,ZHOU W H,SHAN X. An encryption communication scheme based on hardware in circuit –switched domain [J]. Netinfo Security, 2015, 15(6):26—32.(In Chinese)

- [2] 陈颖,陈长松,胡红钢. SM4 硬件电路的功耗分析研究[J]. 信息 网络安全,2018,18(5):52-57.

- CHEN Y, CHEN C S, HU H G. Research on power analysis of SM4 hardware implementation [J]. Netinfo Security, 2018, 18(5):52—57. (In Chinese)

- [3] BANKS D,TOUMAZOU C. Low -power high -speed current comparator design[J]. Electronics Letters, 2008, 44(3):171-172.

- [4] 周成豪,王卫东. 新型电流比较器的设计[J]. 科技信息(科学教研),2007(36):14—16.

ZHOU C H, WANG W D. Design of a new current comparator [J].

Science and Technology Information (Science, Teaching and Research),2007(36):14—16. (In Chinese)

- [5] PALMISANO G, PALUMBO G. High performance CMOS current comparator design [J]. IEEE Transactions on Circuits & Systems II Analog & Digital Signal Processing, 2002, 43(12):785—790.

- [6] GIANNINI V,CRANINCKX J,COME B,et al. 1.5 GHz fully differential latched current comparator with 20 nA of sensitivity[C] //Research in Microelectronics and Electronics. Otranto,Italy: IEEE,2006:181—184.

- [7] 陈卢,石乘学,卢纯. 一种新型的高性能 CMOS 电流比较器电路 [J]. 半导体学报,2001,22(3): 362—365.

CHEN L,SHI B X,LU C. A new high performance CMOS current comparator circuit [J]. Journal of Semiconductors, 2001,22 (3): 362—365. (In Chinese)

- [8] CHAVOSHISANI R, HASHEMIPOUR O. A high -speed current conveyor based current comparator [J]. Microelectronics Journal, 2011,42(1):28—32.

- [9] TRAFF H. Novel approach to high speed CMOS current comparators[J]. Electronics Letters, 1992, 28(3):310—312.

- [10] SRIDHAR R, PANDEY N, BHATTACHARYYA A, et al. High speed high resolution current comparator and its application to analog to digital converter [J]. Journal of the Institution of Engineers, 2016,97(2):1—8.

- [11] BADAL M T I, MASHURI M B, REAZ M B I, et al. Low power high-speed current comparator using 130 nm CMOS technology [C]// 2016 International Conference on Advances in Electrical, Electronic and Systems Engineering (ICAEES). Putrajaya, Malaysia; IEEE, 2017;72—76.