## 一种基于负载检测技术的高稳定性瞬态增强 LDO

谢海情<sup>1,2</sup>,赵欣领<sup>1</sup>,曾健平<sup>3†</sup>,王昌志<sup>1</sup>,巩雅楠<sup>1</sup>,丁宇航<sup>1</sup>,谌运政<sup>1</sup>,刘顺城<sup>1</sup>,梁文萱<sup>1</sup>

(1. 长沙理工大学 物理与电子科学学院, 湖南长沙 410114;

2. 长沙理工大学 柔性电子材料基因工程湖南省重点实验室, 湖南长沙 410114;

3. 湖南大学 物理与微电子科学学院, 湖南长沙 410082)

**摘要:**为提高无片外电容低压差线性稳压器(low-dropout linear regulator, LDO)的瞬态特性,设计优化负载检测电路和过冲/欠冲抑制电路,实现一种低功耗高瞬态特性的无片外电容LDO。负载检测电路通过高比例电流镜采样并跟随LDO负载电流的变化,自适应地改变误差放大器尾电流的大小以改进系统的带宽与摆率,从而提高LDO的瞬态响应速度。在输出电压发生过冲时,过冲抑制电路利用高通网络检测到功率管栅极电压的变化,为负载电流开启放电通路,降低其在输出级的变化量,从而抑制过冲;在输出电压发生欠冲时,欠冲抑制电路通过为功率管栅极驱动电流开启放电通路,快速提高功率管的输出电流,进而有效抑制欠冲。基于0.5 μm CMOS工艺,完成电路设计与测试。结果表明,LDO的输入电压为2~5.5 V,输出电压为1.2 V;电路最大负载电流为150 mA,线性调整率为 $1.7 \times 10^{-3}$ ;无负载时,静态电流小于6.16 μA;负载电流在1~150 mA@1 μs跳变时,欠冲和过冲电压均小于300 mV。该LDO具有功耗低、瞬态特性高等优势,可满足便携式电子设备的应用需求。

**关键词:**低压差线性稳压器;低功耗电子;瞬态分析;负载检测技术;过冲/欠冲抑制

**中图分类号:**TN492      **文献标志码:**A

## A High Stability Transient Enhanced LDO Based on Load Detection Technology

XIE Haiqing<sup>1,2</sup>, ZHAO Xinling<sup>1</sup>, ZENG Jianping<sup>3†</sup>, WANG Changzhi<sup>1</sup>, GONG Ya'nan<sup>1</sup>,

DING Yuhang<sup>1</sup>, CHEN Yunzheng<sup>1</sup>, LIU Shuncheng<sup>1</sup>, LIANG Wenxuan<sup>1</sup>

(1. School of Physics & Electronics Science, Changsha University of Science & Technology, Changsha 410114, China;

2. Hunan Provincial Key Laboratory of Flexible Electronic Materials Genome Engineering, Changsha University of Science & Technology, Changsha 410114, China;

3. School of Physics & Electronics, Hunan University, Changsha 410082, China)

\* 收稿日期:2024-11-15

基金项目:湖南省自然科学基金资助项目(2024JJ7610), Natural Science Foundation of Hunan Province(2024JJ7610);湖南省教育厅科学研究项目(24A0227), Scientific Research Fund of Hunan Provincial Education Department (24A0227);长沙理工大学实践创新与创业能力提升计划项目(CLSJCX23111), Practical Innovation and Entrepreneurship Enhancement Program of Changsha University of Science&Technology(CLSJCX23111);长沙理工大学研究生科研创新项目(CSLGCX23111), Postgraduate Scientific Research Innovation Project of Changsha University of Science&Technology(CSLGCX23111);国家级大学生创新创业训练计划项目(202210536038), National Undergraduate Training Program for Innovation and Entrepreneurship(202210536038)

作者简介:谢海情(1982—),男,湖南永州人,博士,教授,博导

† 通信联系人,E-mail:34907264@qq.com

**Abstract:** To improve the transient characteristics of the output-capacitor less low-dropout linear regulator (LDO), a load detection circuit and overshoot/undershoot suppression circuits are designed and optimized to realize a output-capacitor less LDO with low power consumption and high transient characteristics. By utilizing the high-proportion current mirror to sample and follow the change of the LDO load current, the load detection circuit can adaptively change the tail current of the error amplifier to improve the system's bandwidth and slew rate, thereby enhancing the transient response speed of the LDO. When overshoot occurs in the output voltage, the overshoot suppression circuit utilizes the high-pass network to detect the change of the gate voltage of the power transistor, enabling a discharge path for the load current to reduce its change in the output stage, so as to suppress the overshoot. When the output voltage undershoot occurs, the undershoot suppression circuit can rapidly increase the output current of the power transistor by opening the discharge path for the gate-drive current of the power transistor, and then effectively suppress the undershoot. Based on 0.5  $\mu\text{m}$  CMOS process, the circuit is designed and tested. The results show that the input voltage of the LDO is 2~5.5 V, and the output voltage is 1.2 V; the maximum load current is 150 mA, with the linear regulation of  $1.7 \times 10^{-3}$ ; when there is no load, the quiescent current is less than 6.16  $\mu\text{A}$ ; when the load current varies in 1~150 mA@ 1  $\mu\text{s}$ , both the undershoot and overshoot voltages are less than 300 mV. The LDO has the advantages of low power consumption and high transient characteristics, which can meet the application needs of portable electronic devices.

**Key words:** low-dropout linear regulator; low power consumption electronics; transient analysis; load detection technology; overshoot/undershoot suppression

低压差线性稳压器因其具有低功耗、快速响应、结构简单、易于集成等特性，广泛应用于便携式电子设备<sup>[1-4]</sup>。随着片上系统集成度的提高，传统LDO由于外接电容的存在，不利于片内集成，应用场景受到很大限制，无片外电容LDO成为当前的研究热点<sup>[5-8]</sup>。然而，无片外电容LDO的瞬态响应、环路稳定性等性能不如传统LDO<sup>[9]</sup>。同时，为延长电源寿命而降低功耗的要求常导致无片外电容LDO的瞬态响应进一步变差<sup>[10]</sup>。

为了改善LDO瞬态特性，文献[11]提出了一种具有双向移位寄存器的数字LDO，极大地减少了瞬态响应时间，但功耗较高；文献[12]采用自适应偏置技术设计了一款超低静态电流的LDO，根据负载电流的变化改善LDO的瞬态特性，但在轻载时瞬态响应仍较差；文献[13]提出一种基于翻转电压跟随器（flipped voltage follower，FVF）的无片外电容LDO，结构简单，在低功耗下有更大的带宽与更好的瞬态特性，但其最大负载电流仅为20 mA。为提高LDO的稳定性，文献[14-17]利用内部补偿技术，实现对系统内部主次极点的分离，有效提高系统的稳定性和带宽。

本文提出一种基于负载检测技术的高稳定性瞬

态增强LDO，通过采用负载检测电路检测负载电流的变化，从而调控误差放大器(error amplifier, EA)的摆率与系统的带宽，进而改善LDO的瞬态特性与稳定性；同时引入由检测电路和驱动电路组成的过冲/欠冲抑制电路，其中，检测电路通过检测输出电压的瞬态变化为驱动电路生成控制信号，确保驱动电路仅在瞬态响应期间产生额外的驱动电流，以减少功率管的响应时间与输出电压冲量，进一步提高LDO的瞬态特性。

## 1 LDO 瞬态特性分析

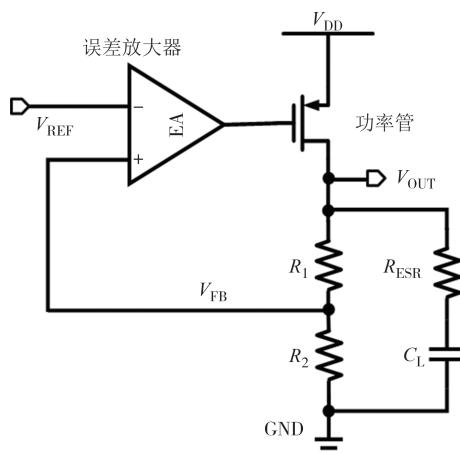

传统LDO基本结构框图如图1所示，其主要由误差放大器、功率管、反馈电阻网络和负载电容构成。其中， $V_{\text{REF}}$ 为基准电压源的输出电压； $V_{\text{FB}}$ 为输出电压 $V_{\text{OUT}}$ 经反馈电阻网络分压后产生的反馈电压；GND表示信号地；输出端外接 $\mu\text{F}$ 级的大电容 $C_L$ ，在负载电流突变时，片外电容能够在功率管响应之前为负载提供充放电流，有效地减小输出电压冲量。

当LDO负载电流突变时，输出电压会产生过冲/欠冲电压。LDO的瞬态特性是指过冲/欠冲电压以及输出电压恢复至稳态所需的响应时间，可表示为：

图 1 传统 LDO 基本结构框图

Fig.1 Basic structure of typical LDO

$$\Delta V = \frac{\Delta I_{\text{load}}}{C_L} \times \Delta t + \Delta I_{\text{load}} \times R_{\text{ESR}} \quad (1)$$

$$\Delta t = \frac{1}{\text{GBW}} + \frac{\Delta V_G}{I_{\text{SR}}} \times C_G \quad (2)$$

式中:  $\Delta V$ 、 $\Delta t$  分别为过冲/欠冲电压大小和瞬态响应时间;  $\Delta I_{\text{load}}$  为负载电流变化量;  $R_{\text{ESR}}$  为 LDO 负载电容

的等效串联电阻; GBW 为 LDO 的单位增益带宽;  $\Delta V_G$  为功率管栅极电压的变化量;  $I_{\text{SR}}$  为功率管栅极的驱动电流;  $C_L$ 、 $C_G$  分别为负载电容与功率管栅极的寄生电容.

由式(1)和式(2)可知, 增大 LDO 的单位增益带宽与功率管栅极驱动电流可以有效减小电压冲量与响应时间, 从而提高瞬态特性.

## 2 LDO 电路设计

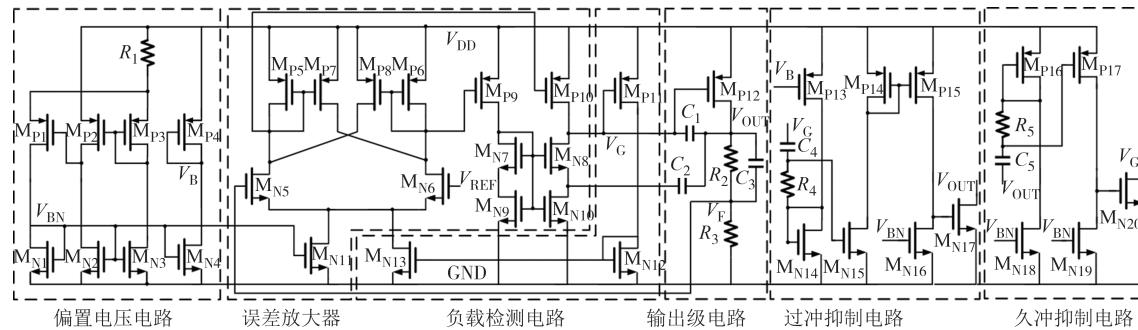

本文设计的无片外电容 LDO 电路结构如图 2 所示,  $M_{P1} \sim M_{P4}$ 、 $M_{N1} \sim M_{N4}$  和电阻  $R_1$  构成偏置电压电路.  $M_{N5}$ 、 $M_{N6}$  和  $M_{N11}$ ,  $M_{P5} \sim M_{P8}$  构成误差放大器第一级, 其中  $M_{P5} \sim M_{P8}$  构成交叉耦合结构, 第二级包括  $M_{N7} \sim M_{N10}$ 、 $M_{P9}$  和  $M_{P10}$ , 其中  $M_{N7} \sim M_{N10}$  为自偏置共源共栅结构.  $M_{N12}$ 、 $M_{N13}$  和  $M_{P11}$  构成负载检测电路.  $C_1$ 、 $C_2$  和  $C_3$  为密勒电容.  $R_2$  和  $R_3$  为反馈电阻网络, 其共同构成输出级电路.  $M_{N14} \sim M_{N17}$ 、 $M_{P13} \sim M_{P15}$ 、电容  $C_4$  以及电阻  $R_4$  构成过冲抑制电路.  $M_{N18} \sim M_{N20}$ 、 $M_{P16}$ 、 $M_{P17}$ 、电容  $C_5$  以及电阻  $R_5$  构成欠冲抑制电路.

图 2 无片外电容 LDO 电路结构图

Fig.2 LDO circuit structure with capacitor-less

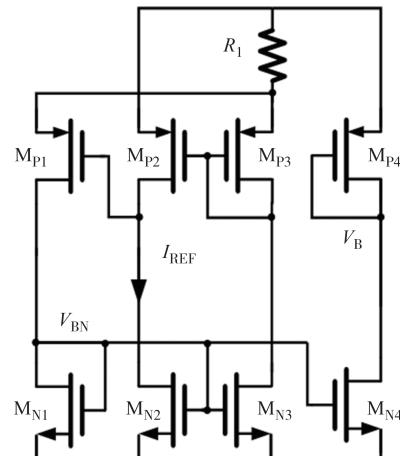

### 2.1 偏置电压电路

偏置电压电路如图 3 所示, 该电路通过为误差放大器和过冲/欠冲抑制电路提供低功耗的偏置电压, 以减小各支路的静态电流, 达到降低静态功耗的目的.

偏置电压电路的 MOS 管均工作于亚阈值区, 其中  $M_{N1}$ 、 $M_{N2}$ 、 $M_{N3}$  和  $M_{N4}$  构成  $1:1:1:1$  电流镜, 且  $I_{\text{REF}}$  为  $M_{N2}$  的漏极电流, 结合亚阈值电流表达式可得到偏置电压  $V_B$  与  $V_{BN}$ :

$$V_B = V_{DD} - mV_T \ln \frac{I_{\text{REF}}}{I_0(W/L)_{M_{P4}}} \quad (3)$$

$$V_{BN} = mV_T \ln \frac{I_{\text{REF}}}{I_0(W/L)_{M_{N1}}} \quad (4)$$

式中:  $W$ 、 $L$  分别为 MOS 管的沟道宽度与沟道长度;  $I_0$

图 3 偏置电压电路

Fig.3 Bias voltage circuit

为单位饱和电流;  $V_T$  为热电压;  $m$  为亚阈值斜率因子;  $V_{DD}$  为电源电压。在保证性能的情况下, 本文  $I_{REF}$  设计取值为 50 nA, 偏置电压电路以此产生偏置电压  $V_B$  与  $V_{BN}$ , 使误差放大器和过冲/欠冲抑制电路在静态时均工作于亚阈值区, 从而降低 LDO 整体电路的静态功耗。

## 2.2 负载检测电路

负载检测电路根据负载电流的变化调控误差放大器尾电流的大小, 以提高 LDO 的瞬态特性。采样管  $M_{P11}$  与功率管  $M_{P12}$  组成高比例电流镜, 空载时, 采样得到的动态偏置电流很微弱, 较小的固定尾电流使误差放大器保持低的静态功耗。当负载电流增大时, LDO 的系统带宽以及误差放大器的摆率可表示为:

$$\text{GBW} = \frac{2I_{D1}r_{o1}g_{m, MP10}}{V_{OV, MN5}[(C_1 + g_{m, MN8}r_{o2}C_2)]} \quad (5)$$

$$\text{SR} = \frac{K_1 I_{D1}}{g_{mp}r_{op}(C_1 + g_{m, MN8}r_{o2}C_2)} \quad (6)$$

式中:  $I_{D1}$  为  $M_{N11}$  与  $M_{N13}$  的漏极电流之和;  $g_{m, MN8}$ 、 $g_{m, MP10}$  和  $g_{mp}$  分别为  $M_{N8}$ 、 $M_{P10}$  和  $M_{P12}$  的等效跨导;  $V_{OV, MN5}$  为  $M_{N5}$  的过驱动电压;  $r_{o1}$ 、 $r_{o2}$  和  $r_{op}$  分别为误差放大器第一级、 $M_{N10}$  和  $M_{P12}$  的输出阻抗;  $K_1$  为  $M_{P10}$  与  $M_{P5}$  的宽长比之比, 取值为 0.5。

由式(5)和式(6)可得, 随着负载电流的增加,  $M_{N13}$  为误差放大器提供的动态偏置电流增加, 较大的动态偏置电流增大了误差放大器的摆率, 同时也增大了系统的带宽, 使  $M_{P12}$  快速响应, 进而减小 LDO 的响应时间。

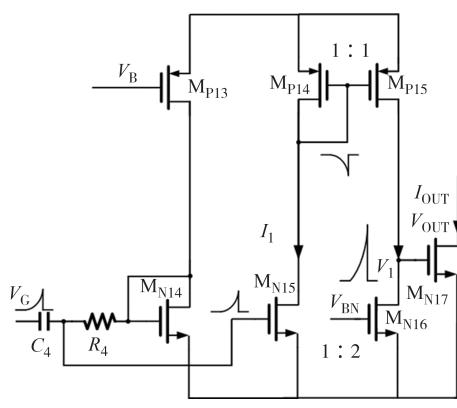

## 2.3 过冲抑制电路

过冲抑制电路如图 4 所示。

Fig.4 Overshoot suppression circuit

当 LDO 处于稳态时,  $M_{N15}$ 、 $M_{P14}$  和  $M_{P15}$  同时工作在亚阈值区,  $M_{P14}$ 、 $M_{P15}$  的宽长比为 1:1,  $M_{N15}$ 、 $M_{N16}$  的宽长比为 1:2,  $M_{N16}$  将电压  $V_1$  下拉至地, 此时  $M_{N17}$  处于截止状态。当负载电流由重载突变为轻载时, 输出电压  $V_{OUT}$  出现过冲电压并反馈至  $M_{P12}$  棚极。 $M_{P12}$  棚极电压  $V_G$  升高并通过电阻  $R_4$  和电容  $C_4$  组成的 RC 高通网络使  $M_{N15}$  的漏极电流  $I_1$  迅速增大, 该电流通过电流镜使得  $M_{P15}$  的上拉能力增强。随着  $V_G$  继续升高,  $V_1$  开始发生跳变, 跳变的阈值为:

$$\Delta V_{G, \text{trigger}} = 2V_T \sqrt{m \exp\left(\frac{V_{OV, MP15}}{mV_T}\right) - |V_{OV, MP15}|} \quad (7)$$

式中:  $\Delta V_{G, \text{trigger}}$  的设计取值为 30 mV, 在保证抑制电路灵敏度的同时, 也为工艺角的变化留一定裕度。

$V_1$  迅速升高,  $M_{N17}$  随即导通并为  $M_{P12}$  漏极提供放电电流:

$$I_{OUT} = g_{m, MN17} A_{MN15} A_{MP15} (\Delta V_G - \Delta V_{G, \text{trigger}}) \quad (8)$$

式中:  $A_{MN15} = g_{m, MN15} r_{o3}$ ;  $A_{MP15} = g_{m, MP15} r_{o4}$ ;  $r_{o3}$ 、 $r_{o4}$  分别为  $M_{N15}$ 、 $M_{P15}$  的输出阻抗;  $\Delta V_G$  为  $M_{P12}$  棚极电压的变化量。

由式(8)可知,  $M_{N17}$  提供的放电通路减小负载电流在输出级的变化量, 可以有效地抑制 LDO 的过冲电压。电路进入稳态后,  $M_{N15}$ 、 $M_{P14}$  和  $M_{P15}$  再次进入亚阈值区, 减小电流消耗。

## 2.4 欠冲抑制电路

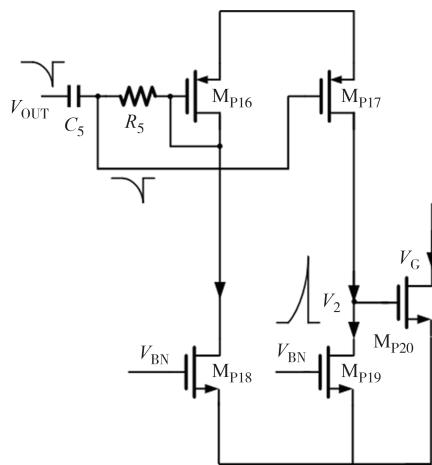

当负载电流由轻载突变为重载时, 输出电压  $V_{OUT}$  出现欠冲电压, 抑制电路需要采用与  $M_{P12}$  面积相当的 PMOS 管来为负载提供额外的电流, 以达到较好的抑制效果。根据式(2), 可为  $M_{P12}$  棚极驱动电流提供一条放电通路来抑制欠冲电压, 欠冲抑制电路如图 5 所示。

与过冲抑制电路类似, 当 LDO 处于稳态时, 电压  $V_2$  接近地,  $M_{N20}$  处于截止状态。当 LDO 的负载电流突增时, 欠冲电压通过高通网络使  $M_{P17}$  从亚阈值区进入饱和区, 流经  $M_{P17}$  的电流迅速增大, 从而使得电压  $V_2$  迅速升高,  $M_{N20}$  随即开启并为  $M_{P12}$  棚极提供放电通路, 进而有效抑制 LDO 的欠冲电压。

## 3 环路稳定性分析

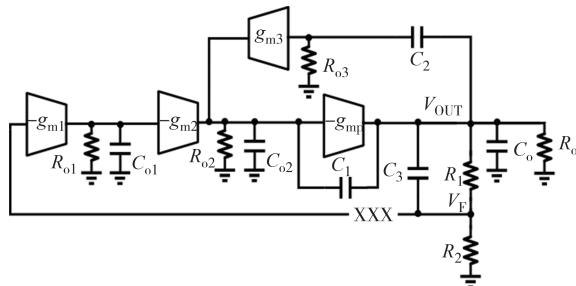

### 3.1 稳态环路稳定分析

LDO 的等效小信号模型如图 6 所示。图中  $g_{m1}$ 、 $g_{m2}$ 、 $g_{m3}$  和  $g_{mp}$  分别表示误差放大器第一级、第二级、

图 5 欠冲抑制电路

Fig.5 Undershoot suppression circuit

$M_{N8}$  和  $M_{P12}$  的等效跨导,  $R_{oi}$  和  $C_{oi}$  分别表示各个节点的等效阻抗和等效电容,  $C_i$  表示密勒电容,  $R_i$  表示反馈电阻. 图中“XXX”指信号通路断开.

图 6 等效小信号模型

Fig.6 Equivalent small signal model

由图 6 得到 LDO 的开环传输函数:

$$A(s) =$$

$$\frac{g_{m1}R_{o1}g_{m2}R_{o2}g_{mp}R_o \left(1 + \frac{s}{\omega_{z1}}\right) \left(1 + \frac{s}{\omega_{z2}}\right)}{\left(1 + \frac{s}{\omega_{p1}}\right) \left(1 + \frac{s}{\omega_{p2}}\right) \left(1 + \frac{s}{\omega_{p3}}\right) \left(1 + \frac{s}{\omega_{p4}}\right) \left(1 + \frac{s}{\omega_{p5}}\right)} \quad (9)$$

式中: $s$  为复频率;  $\omega_{pi}$  ( $i=1 \sim 5$ ) 为极点频率;  $\omega_{zi}$  ( $i=1 \sim 2$ ) 为零点频率.

电路存在 5 个极点, 分别为:

$$\omega_{p1} = \frac{1}{[g_{mp}R_o(g_{m3}R_{o3}C_2 + C_1) + C_{o2}]R_{o2}} \quad (10)$$

$$\omega_{p2} = \frac{C_1g_{mp}}{C_o(C_1 + C_{o2})} \quad (11)$$

$$\omega_{p3} = \frac{1}{R_{o1}C_{o1}} \quad (12)$$

$$\omega_{p4} = \frac{g_{m3}}{C_1} \quad (13)$$

$$\omega_{p5} = \frac{1}{(R_1||R_2)C_2} \quad (14)$$

式中:  $g_{mp}R_o(g_{m3}R_{o3}C_2 + C_1) \gg C_{o2}$ , LDO 的单位增益带宽可以表示为:

$$GBW = \frac{g_{m1}R_{o1}g_{m2}}{g_{m3}R_{o3}C_2 + C_1} \quad (15)$$

高频极点  $\omega_{p3}$ 、 $\omega_{p4}$  和  $\omega_{p5}$  在单位增益带宽之外, 对电路稳定性无影响. 然而, 随着负载电流  $I_{load}$  增加,  $M_{P12}$  的等效跨导  $g_{mp}$  随之增大, 而由负载电流经高比例电流镜产生的动态偏置电流使误差放大器的输出阻抗  $R_{o2}$  缓慢减小. 因此, 由式(10)和式(11)可知, 极点  $\omega_{p1}$  和  $\omega_{p2}$  会跟随负载电流的增大远离原点, 但次极点  $\omega_{p2}$  的步进更大. 当负载电流为 0 时, 主、次极点最为接近, 致使系统的相位裕度(phase margin, PM)最差. 根据式(11)和式(15), 可通过调节密勒电容  $C_1$  和  $C_2$ , 将次极点置于 2 倍单位增益带宽之外:

$$\frac{C_1g_{mp}}{C_o(C_1 + C_{o2})} \geq \frac{2g_{m1}R_{o1}g_{m2}}{g_{m3}R_{o3}C_2 + C_1} \quad (16)$$

在满足式(16)时, 可使 LDO 系统稳定, 其中密勒电容  $C_1$  和  $C_2$  取值为 8.6 pF 和 2.6 pF. 随着负载电流增大, 次极点逐渐远离主极点, 系统的相位裕度增加, 稳定性逐步提高.

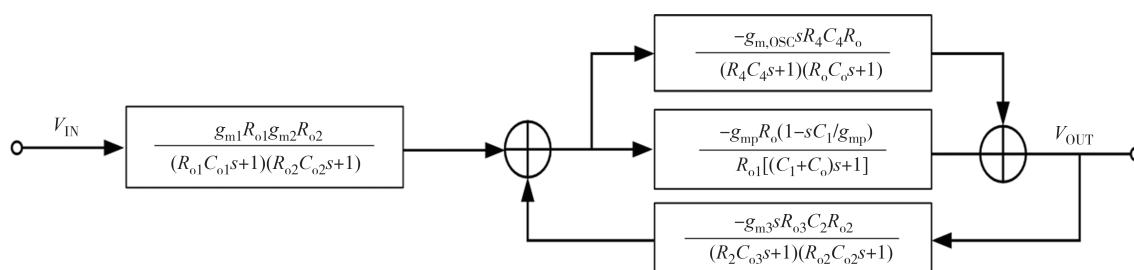

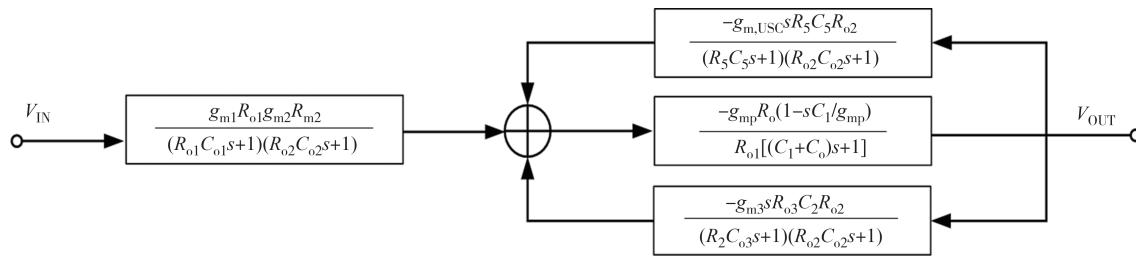

### 3.2 瞬态环路稳定分析

当抑制电路启动时, 电路的等效小信号分析如图 7 所示.

(a) 过冲抑制电路启动时等效小信号分析图

(b)欠冲抑制电路启动时等效小信号分析图

图 7 抑制电路启动时等效小信号分析图

Fig.7 Diagram of the equivalent small signal analysis at the start-up of the suppression circuit

忽略高频零、极点，在过冲抑制电路启动时，电路的主、次极点分别为：

$$\omega_{p1,OSC} = \frac{1}{g_{mp} R_o (g_{m3} R_{o3} C_2 + C_1) R_{o2}} \quad (17)$$

$$\omega_{p2,OSC} = \frac{C_1 (g_{mp} + g_{m,OSC})}{C_o (C_1 + C_{o2})} \quad (18)$$

在欠冲抑制电路启动时，电路的主、次极点分别为：

$$\omega_{p1,USC} = \frac{1}{g_{mp} R_o (g_{m3} R_{o3} C_2 + g_{m,USC} R_5 C_5) R_{o2}} \quad (19)$$

$$\omega_{p2,USC} = \frac{C_1 g_{mp}}{C_o (C_1 + C_{o2})} \quad (20)$$

式中： $g_{m,OSC}$ 、 $g_{m,USC}$  分别为过冲抑制电路和欠冲抑制电路的等效跨导。

对比抑制电路启动前后的主、次极点位置变化可知，在启动之后，过冲抑制电路使次极点远离原点，欠冲抑制电路使主极点向原点移动，主、次极点分离，进一步提高 LDO 的稳定性。

## 4 仿真与测试结果分析

### 4.1 仿真结果与分析

基于  $0.5 \mu\text{m}$  CMOS 工艺，利用 Spectre 等工具对电路进行仿真分析。

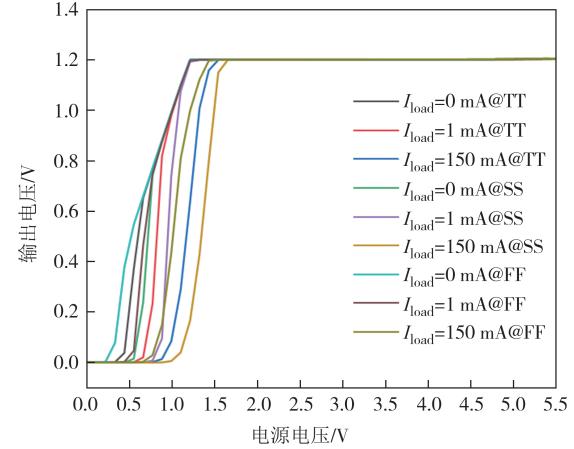

图 8 为 LDO 的线性调整率特性曲线，在工艺角为 TT、SS 和 FF，负载电流  $I_{load}$  为 0、1、150 mA 时，线性调整率最小为  $0.6 \times 10^{-3}$ ，最差为  $1.84 \times 10^{-3}$ 。

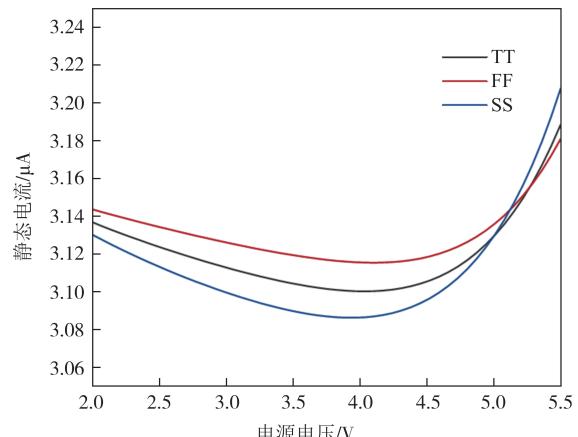

图 9 为 LDO 的静态电流在工艺角为 TT、SS 和 FF 时随电源电压变化的仿真曲线。在电源电压为 2~5.5 V 的工作范围内，静态电流为  $3.086 \sim 3.179 \mu\text{A}$ 。

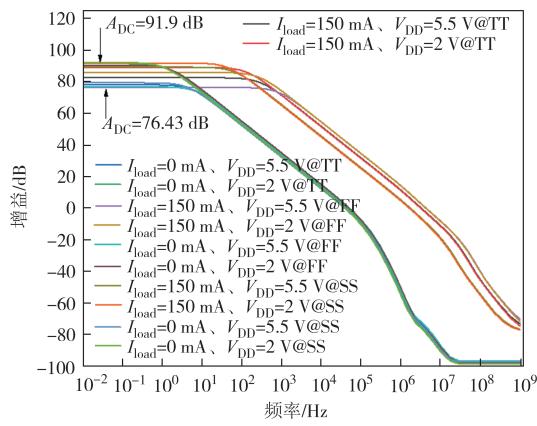

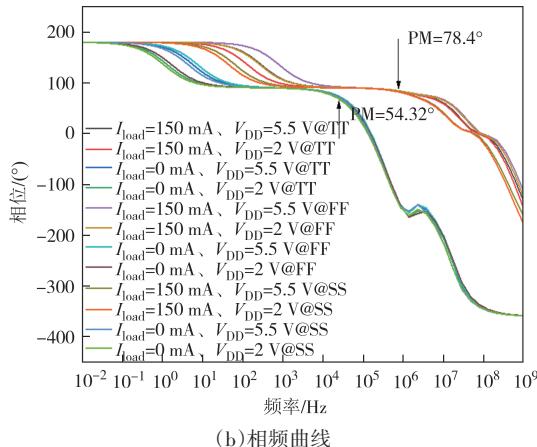

图 10 为 LDO 在负载电流  $I_{load}$  为 0 mA 和 150 mA，电源电压  $V_{DD}$  为 2 V 和 5.5 V，工艺角为 TT、FF 和 SS 时的稳定仿真曲线，LDO 的最小低频环路增益  $A_{dc}$  大于 70 dB，在负载电流为 0 时，带宽最小为 32.3 kHz，相

图 8 线性调整率特性曲线

Fig.8 Characteristic curves of linear regulation

图 9 静态电流仿真曲线

Fig.9 Simulation curves of quiescent current

位裕度 PM 最差为  $54.32^\circ$ 。随着负载电流增大，由式 (15) 可知，单位增益带宽随之增大，同时相位裕度也逐渐改善，满载时，带宽最小为 2.3 MHz，相位裕度为  $78.4^\circ$ ，LDO 具有良好的稳定性。

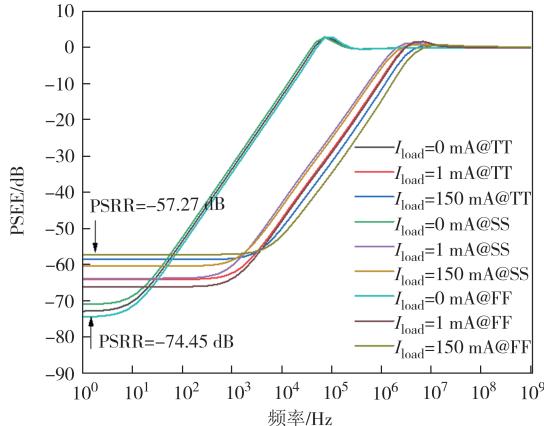

图 11 为 LDO 在负载电流  $I_{load}$  为 0、1 和 150 mA 时的电源抑制比 (power supply rejection ratio, PSRR) 特性曲线。得益于高环路增益，该 LDO 具有高 PSRR。在不同工艺角、负载电流下，低频下的 PSRR 最低为

(a) 增益曲线

(b) 相频曲线

图 10 不同条件下稳定性仿真曲线

Fig.10 Simulation curves of stability under different conditions

-74.45 dB, 最差为 -57.27 dB, LDO 对电源噪声有较好的抑制能力.

图 11 电源抑制比特性曲线

Fig.11 Characteristic curves of power supply rejection ratio

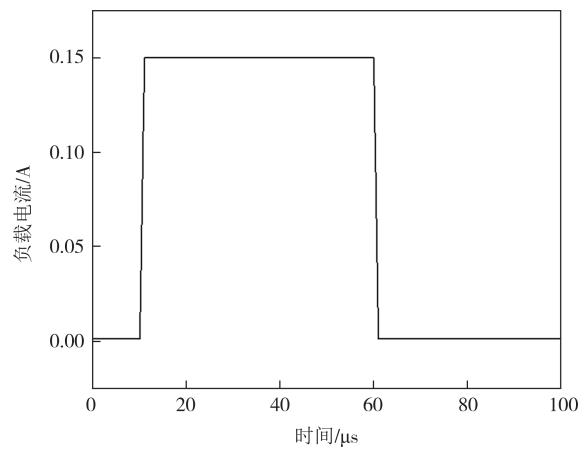

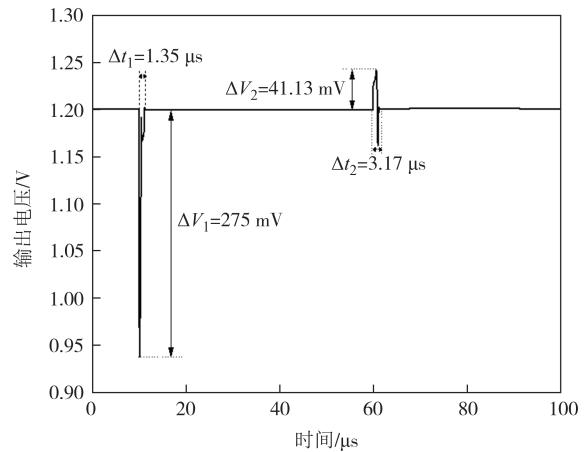

图 12 为 TT 工艺角下 LDO 的瞬态响应特性曲线. 负载电流从 1~150 mA 以 1  $\mu$ s 的时间阶跃变化, LDO 的欠冲响应时间  $\Delta t_1$  为 1.35  $\mu$ s, 欠冲电压  $\Delta V_1$  为 275 mV; 过冲响应时间  $\Delta t_2$  为 3.17  $\mu$ s, 过冲电压  $\Delta V_2$  为 41.13 mV.

(a) 负载电流阶跃变化曲线

(b) LDO 输出电压瞬态特性曲线

图 12 瞬态响应特性曲线

Fig.12 Characteristic curve of transient response

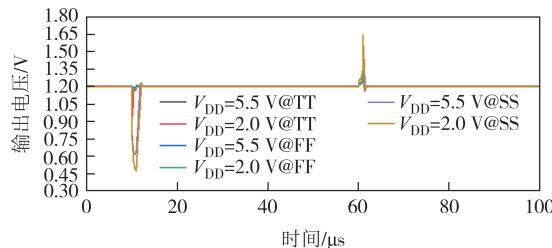

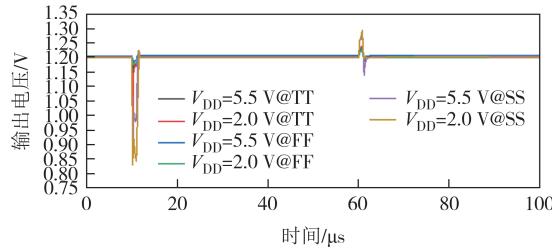

考虑到工艺、电源电压的影响, LDO 在工艺角为 TT、FF 和 SS, 电源电压  $V_{DD}$  为 2 V、5.5 V 时的瞬态响应特性曲线如图 13 所示. 图 13(a) 表示无抑制电路时 LDO 的瞬态响应曲线, 欠冲/过冲电压最大为 730 mV/483 mV. 图 13(b) 表示增加抑制电路后 LDO 的瞬态响应曲线, 欠冲/过冲电压最大为 435 mV/101 mV. 由图 13(a) 和 13(b) 对比可知, 欠冲电压减少 295 mV, 过冲电压减少 382 mV, 抑制电路显著降低电压冲量, 有效提高 LDO 的瞬态特性.

#### 4.2 测试结果与分析

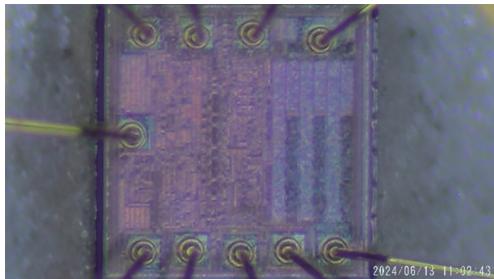

基于 0.5  $\mu$ m CMOS 工艺, 完成芯片流片, 图 14 为芯片的显微镜照片.

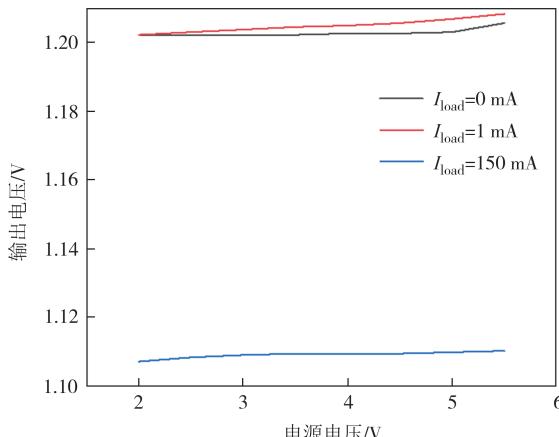

图 15 为 LDO 的线性调整率测试结果, 在负载电流  $I_{load}=0, 1, 150$  mA 时, 线性调整率分别为  $0.9 \times 10^{-3}$ 、 $1.7 \times 10^{-3}$  和  $0.8 \times 10^{-3}$ , 与仿真结果吻合较好.

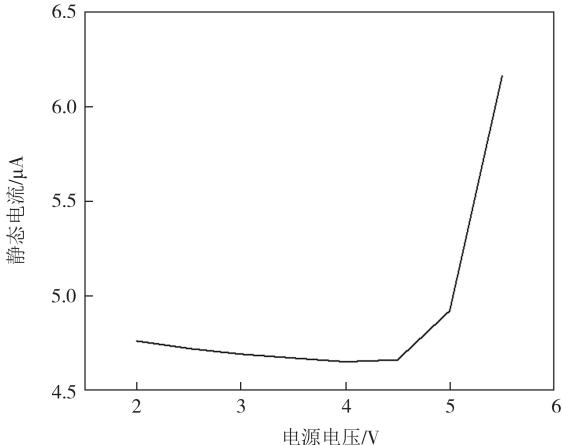

图 16 为 LDO 的静态电流随电源电压变化的测试结果. 在电源电压为 2~5.5 V 的工作范围内, 静态电流为 4.65~6.16  $\mu$ A. 静态电流的测试结果与仿真

(a) 无抑制电路的LDO瞬态响应

(b) 有抑制电路的LDO瞬态响应

图 13 不同条件下的瞬态响应特性曲线

Fig.13 Characteristic curves of transient response under different conditions

图 14 芯片的显微镜照片

Fig.14 Microscopic photograph of the chip

图 15 线性调整率测试结果

Fig.15 Test results of linear regulation

结果具有一定的偏差,可能原因为电阻的工艺制造误差使偏置电压电路的电阻 $R_1$ 、输出支路的反馈电阻 $R_2$ 和 $R_3$ 的阻值偏低,进而导致静态电流偏高。

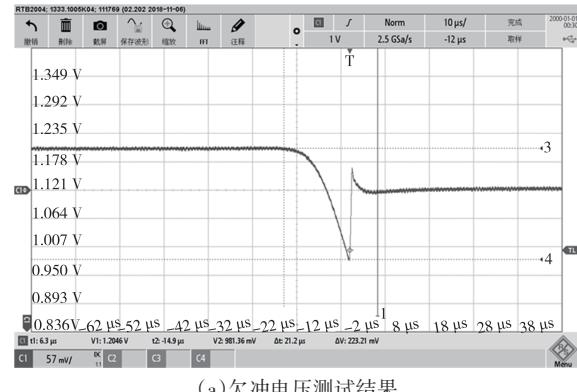

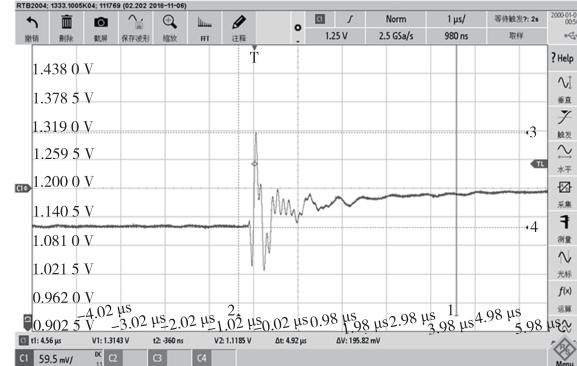

图 17 为 LDO 瞬态特性测试结果,负载电流从 1~150 mA 以 1  $\mu$ s 的时间阶跃变化,测得欠冲电压为

223 mV,过冲电压为 195 mV。过冲电压的测试结果与仿真结果有一定偏差,可能原因为硅片输出端引脚与封装引脚之间的导线阻抗较大,重载时,LDO 的输出电压产生额外的压降,从而导致过冲电压增大,然而 LDO 仍具有良好的瞬态特性。

图 16 静态电流测试结果

Fig.16 Test results of quiescent current

(a) 欠冲电压测试结果

(b) 过冲电压测试结果

图 17 瞬态响应测试结果

Fig.17 Test results of transient response

表 1 为本文芯片与其他文献中 LDO 的性能对比。可以看出,本文设计的 LDO 芯片在保证良好瞬态响应的同时,静态功耗方面明显优于文献[1]和[16]。

对比文献[17],本芯片引入了抑制电路,通过牺牲静态电流以提高瞬态特性.因此,虽然本芯片的功耗

稍高于文献[17],但过冲电压较文献[17]有较大改进.

表 1 性能对比

Tab.1 Performance comparison

| 文献   | 工艺/ $\mu\text{m}$ | 电源电压/V  | 输出电压/V | 最大负载电流/mA | 静态电流/ $\mu\text{A}$ | 线性调整率/( $10^{-3}$ ) | 欠冲电压/mV | 过冲电压/mV |

|------|-------------------|---------|--------|-----------|---------------------|---------------------|---------|---------|

| [1]  | 0.5               | 2.2~2.7 | 2      | 100       | 270                 | 2.2                 | 310     | 200     |

| [16] | 0.35              | 2.7~3.3 | 2.5    | 100       | 66                  | 0.8                 | 225     | 170     |

| [17] | 0.5               | 3.5~6   | 3.3    | 100       | 4.5                 | —                   | —       | 600     |

| 本文   | 0.5               | 2~5.5   | 1.2    | 150       | 6.16                | 1.7                 | 223     | 195     |

## 5 总结

本文设计优化负载检测电路和过冲/欠冲抑制电路,实现一种低功耗高稳定性的瞬态增强无片外电容 LDO. 负载检测电路能够自适应地改变误差放大器的尾电流的大小,提高 LDO 的瞬态响应速度;过冲抑制电路能够为负载电流提供放电通路,抑制过冲;欠冲抑制电路为功率管栅极提供放电通路,抑制欠冲. 基于 0.5  $\mu\text{m}$  CMOS 工艺,完成 LDO 电路设计与流片测试. 结果表明,当输入电压为 2~5.5 V 时,LDO 芯片最大负载电流为 150 mA,输出电压为 1.2 V,线性调整率为  $1.7 \times 10^{-3}$ ;无负载时,静态电流小于 6.16  $\mu\text{A}$ ;负载电流在 1~150 mA@1  $\mu\text{s}$  跳变时,过冲和欠冲电压均小于 300 mV. 该 LDO 芯片具有功耗低、稳定性高、瞬态特性高等优势,可很好地满足便携式电子设备的应用需求.

## 参考文献

- [1] 张文林,张家豪,明鑫,等.一种低压快速瞬态响应的片上 LDO[J].微电子学,2018,48(3):364~369.

ZHANG W L, ZHANG J H, MING X, et al. A low voltage fast transient response on-chip LDO [J]. Microelectronics, 2018, 48(3):364~369. (in Chinese)

- [2] 黄祥林.一种应用于蓝牙耳机的低功耗 LDO 设计[D].苏州:苏州大学,2022.

HUANG X L. A low-power LDO design for bluetooth headset[D]. Suzhou: Soochow University, 2022. (in Chinese)

- [3] PEREIRA-RIAL Ó, LÓPEZ P, CARRILLO J M. 0.6-V-VIN 7.0-nA-IQ 0.75-mA-IL CMOS capacitor-less LDO for low-voltage micro-energy-harvested supplies [J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2022, 69 (2) : 599~608.

- [4] AKRAM M A, HONG W, HA S, et al. Capacitor-less dual-mode all-digital LDO with  $\Delta\Sigma$ -modulation-based ripple reduction [J]. IEEE Transactions on Circuits and Systems II : Express Briefs, 2021, 68(5):1620~1624.

- [5] LEE C K, LEE C H, JEON Y J, et al. A 92 ns settling-time fast-transient capacitor-less LDO with a stable class B bandwidth-boosting error amplifier and an improved buffer for mobile applications [J]. IEEE Transactions on Industrial Electronics, 2024, 71(9):11696~11700.

- [6] PARK H, JUNG W, KIM M, et al. A wide-load-range and high-slew capacitor-less NMOS LDO with adaptive-gain nested miller compensation and pre-emphasis inverse biasing [J]. IEEE Journal of Solid-State Circuits, 2023, 58(10):2696~2708.

- [7] LIMPISAWAS T, WATTANAPANITCH W. A low-power wide-load-range output-capacitorless low-dropout voltage regulator with indirect-direct nested miller compensation [J]. IEEE Access, 2022, 10: 67396~67412.

- [8] KAO S K, CHEN J J, LIAO C H. A multipath output-capacitor-less LDO regulator [J]. IEEE Access, 2022, 10:27185~27196.

- [9] CHENG T D, XIAO Z Y, GUO J P, et al. A low power high area-efficiency NMOS LDO with fast adaptive bias [J]. Integration, 2023, 88:371~378.

- [10] BOANLOO M M, YAVARI M. A push-pull FVF based LDO voltage regulator with slew rate enhancement at the gate of power transistor [J]. Microelectronics Journal, 2022, 122:105389.

- [11] AKRAM M A, HONG W, HWANG I C. Capacitorless self-clocked all-digital low-dropout regulator [J]. IEEE Journal of Solid-State Circuits, 2019, 54(1):266~276.

- [12] 王媛,汪西虎.一种超低静态电流 LDO 线性稳压器的设计[J].半导体技术,2022,47(2):145~151.

WANG Y, WANG X H. Design of an ultra-low quiescent current LDO linear regulator [J]. Semiconductor Technology, 2022, 47(2): 145~151. (in Chinese)

- [13] 陈俊杰,袁磊,陈子杰,等.一种无片外电容高瞬态响应LDO设计[J].中国集成电路,2023,32(3):26–30.

- CHEN J J, YUAN L, CHEN Z J, et al. An output-capacitorless low-dropout regulator with fast transient response [J]. China Integrated Circuit, 2023, 32(3):26–30.(in Chinese)

- [14] 刘云超,陈敏,刘云涛,等.低功耗自适应偏置无片外电容低压差稳压器[J].湖南大学学报(自然科学版),2018,45(10):93–101.

- LIU Y C, CHEN M, LIU Y T, et al. Low-power adaptively biased output-capacitor-free low-dropout regulator[J]. Journal of Hunan University (Natural Sciences) , 2018, 45 (10) : 93–101. (in Chinese)

- [15] BANSAL R, CHATTERJEE S. A 22-nA quiescent current, 50-ma output-capacitor-less low-dropout regulator with multiple-feedback loop for iot devices [J]. IEEE Transactions on Circuits and Systems II : Express Briefs, 2024, 71(11):4608–4612.

- [16] MING X, KUANG J J, GONG X C, et al. A fast-transient capacitorless LDO with dual paths active-frequency compensation scheme [J]. IEEE Transactions on Power Electronics, 2022, 37(9): 10332–10347.

- [17] 崔传荣,巩文超,王忆,等.低功耗无片外电容的低压差线性稳压器[J].浙江大学学报(工学版),2009,43(11): 2006–2011.

- CUI C R, GONG W C, WANG Y, et al. Low dropout linear regulator with no off-chip capacitor and low power consumption [J]. Journal of Zhejiang University (Engineering Science) , 2009, 43(11):2006–2011. (in Chinese)